# **APX**press Whitepaper

# 1. Zonal architectures

The increasing integration of sensors for environment recognition and displays for visualisation characterises modern driver assistance systems. This is accompanied by a significant increase in data transfer volume in the vehicle, easily reaching 600 Gbps or more. Reliable and economical transmission of this data is becoming a key challenge.

Current control units have millions of lines of code. In view of the large number of such control units and the resulting complexity of the network, a redesign of hardware and software functions is immanent. Lidar and radar play a key role, supported by cameras for real-time environment detection. The fusion of this data to an environment model forms the basis for assistance systems and autonomous driving. This requires synchronised, low-latency and low jitter forwarding of the sensor data to the processing units.

Today, high speed sensors are integrated in a domain-based architecture. The vehicle is divided into different domains of type of functionality. Such domains are powertrain, body or infotainment. Zonal architectures on the other hand, divide the vehicle into local zones with different type of functions and thus offer a more efficient use of resources such as computing power, energy, and memory.

The growing complexity of assistance systems, particularly for autonomous driving, means that the domains are distributed across the entire vehicle. This leads to complex networking, with the wiring harness being the heaviest component apart from the engine. A zonal architecture offers the advantage of significantly reducing the weight and complexity of the wiring harness.

In zonal architectures, the functionality shifts away from domain controllers to zonal control units and to a central processor. Functions are grouped according to their location in the vehicle.

Data transmission in zonal architectures is characterised by the handling of a wide variety of data types with very diverse bandwidths and security requirements.

# 2. APXpress - A scalable high-speed network for zonal architectures

Key elements for a scalable high-speed network in zonal architectures are variable link bandwidth, flexible security concepts, configurability and bundling of different data streams as well as support for different physical transmission media.

The configurability of the network is essential. The ability to configure the network according to specific needs and requirements is a prerequisite for a "software-defined" network. Zonal architectures require an adaptable data path architecture to accommodate different application profiles and traffic requirements.

The support of different physical transmission media is fundamental to seamlessly integrating different technologies. Zonal architectures can make use of various media such as wire or fiber optics. The ability to adapt to different media helps to consider the space requirements and constraints in the vehicle and ensure optimal performance.

APXpress is a technology based on data transmission with data cells and has some similarities to ATM (Asynchronous Transfer Mode). It can support up to 512 completely independent data channels (virtual data paths). The latency of each virtual data path is controllable and deterministic. Due to the cell-based transmission technology, the bandwidth can be (dynamically) allocated for each channel.

APX press technology decouples the SerDes or link bandwidth from the (aggregated) bandwidth of the virtual data paths.

APX press is scalable and works with link data rates of 4/8/16 or 32 Gbps. The transmission of all virtual data paths are reliably protected by a patented FEC/line code.

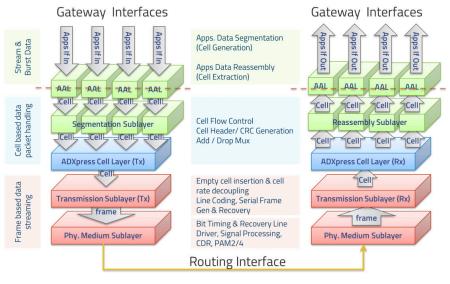

Figure1: APXpress communication layers

Data are packed and unpacked using generic hardware blocks without any software. APXpress technology is characterised by extremely low-power dissipation, achieved through optimised line code/FEC, hardware packaging and analogue PHYs.

APX press consists of three communication layers, with gateway interfaces connected to the AAL (APXpress Application Layer). The ACL (APXpress Cell Layer) that includes cell flow control and distribution as well as cell routing with CRC for data integrity. Line coding, serial frame generation, bit re-timing and recovery, line drivers and CDR implementation as a routing interface take place in the physical APL (APXpress Physical Layer).

# 3. Virtual data paths - the principle for a configurable hardware platform for secure high-speed data transmission

APX press technology is based on virtual data paths, which are realised by transmitting data cells of constant size. In contrast to IP, all cells take the same path through the network, which results in constant latency and jitter on each virtual path.

Virtual paths have the big advantage that they can be used as multiplexing layers for different services (video, audio, ether-net), as the properties of the virtual paths can be configured individually without interfering with the other virtual paths.

Virtual data paths only consume bandwidth when user data is being transmitted. APXpress offers 512 virtual, full-duplex data paths. Each virtual data path allows dynamic bandwidth allocation each of which can be assigned bandwidth dynamically.

A virtual data path is created by segmenting application data into cells at the gateway interface. Each cell receives security information and a Virtual Path Identifier (VPI) as the source address. The assignment of port and virtual path is configurable. In the APX press module, cells are merged into a data stream on the cell layer, serialised on the physical layer and fed to the routing interface.

Forwarding in the APX press network is based on the virtual path address and is configurable. This way, application data is forwarded from a specific input to one specific or several outputs (multi drop).The application interfaces are terminated at the gateway interfaces, where the application data is extracted, packed and transported. This allows a kind of "bridging" between

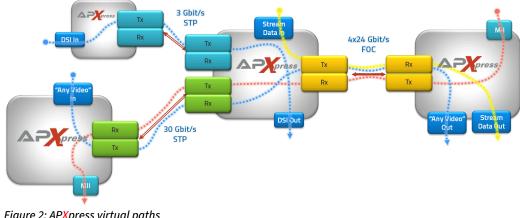

Figure 2: APX press virtual paths

different application interfaces. Video data can be received via the DisplayPort interface and then sent via a DSI interface. The termination decouples latency, speed and format from the transmission system.

The ACL and the APL supports a multi-lane architecture. This enables serial transmission over one or more links to increase bandwidth. Redundant cell data streams can be transmitted over independent physical media to compensate for a complete failure of one serial link.

Cell data transmission enables deterministic control of latency by multiplexing on the ACL. This reduces the memory requirement for redundant cell data streams and enables the synchronisation of cell data streams from different application interfaces such as lidar and camera.

## 4. Generic gateway interfaces - HW for packaging any data with the very low latency

Application data is received and sent at the gateway interfaces via the corresponding (hardware) application interfaces. The gateway interfaces form the interface to the application are an integral part of the AAL (APX press Application Layer).

Two basic paradigms are implemented in this layer. First, cell data is packaged exclusively in HW. SW-based packaging would be inefficient and would require a considerable amount of compute resources. Second, the application interfaces are always terminated, which means that they are not tunnelled through the APX press system. Only Data is transferred without the bus protocol to decouple the properties of the application interface from the subsequent data transport system.

## 5. APXpress - Physical Layer - A multi-bandwidth and multi-media transmission system

The APX press Physical Layer is the bridge between the APX press Cell Layer and the transmission medium. Media themselves can be either electrical or optical. Electrical media can be coax or SPP (Shielded Parallel Pair). Optical media require a converter from electrical to optical. To be able to transport the data of the APX press cell layer (ACL) to the respective remote station, the steps listed below are necessary.

#### Transmit side:

1. Insertion of empty cells to generate a continuous cell data stream (decouples the cell rate from the link rate)

- 2. FEC encoding with bandwidth adjustment due to overhead

- 3. Line coding

4. PMA (Physical Medium Attachment): Serialisation and modulation using line drivers

#### Receive side:

1. PMA (Physical Medium Attachment): Demodulation with subsequent EQ/DFE/clock recovery and deserialisation

- 2. Alignment and line decoding

- 3. FEC decoding with symbol correction, if required

- 4. Removal of empty cells

This sequence has several advantages:

Applying the FEC before line coding ensures that the bit sequences on the transmission medium always fulfil the desired characteristics of run length, DC balance, and transition density. This is particularly important for long copper cables to be able to reconstruct the data on the receiver side without errors. It is also possible to choose between two different FECs. One can choose between strong protection with more overhead or weaker protection with less overhead. A patented form of line coding ensures that individual bit errors can never harm more than one FEC symbol. This in turn enables an extremely efficient FEC implementation that protects the entire link from bit errors and thus achieves the desired bit error rate (BER). The global FEC also makes an application-specific FEC obsolete. A side effect of the global FEC is the possibility of very precise link monitoring, which is used to adapt the link during operation to guarantee sufficient link margin.

|                       | Use Case                | Performance                                            | <b>Bandwidth</b><br>[Gbit/s]         | PLL Struktur | Modulation | Phy. Media               | Phy. Int<br>Clock  | terface<br>Full Duplex |

|-----------------------|-------------------------|--------------------------------------------------------|--------------------------------------|--------------|------------|--------------------------|--------------------|------------------------|

| ROUTING<br>INTERFACES | APXpress<br>Serial Link | HIGHEST<br>Cable, <b>long range</b><br>NRZ BER < 10-13 | 32,0000<br>16,0000<br>8,0000         | Integer      | NRZ        | COAX,<br>STP, SPP<br>FOC | Embedded<br>Clock  | dual simplex           |

|                       |                         |                                                        | 4,0000                               |              |            |                          |                    |                        |

|                       |                         | MEDIUM<br>FOC Modules                                  | 28,0000<br>26,5625                   | Fractional   | NRZ        | PCB<br>TRACES            | Embedded<br>Clock  | dual simplex           |

|                       |                         |                                                        | 10,3125                              |              |            |                          |                    |                        |

| GATEWAY<br>INTERFACES | PCI Express             | MEDIUM<br>PCB Traces,<br>Chip to chip If               | 32,0000<br>16,0000<br>8,0000         | Integer      | NRZ        | PCB<br>TRACES            | Separated<br>Clock | dual simplex           |

|                       |                         |                                                        | 5,0000                               | Fractional   |            |                          |                    |                        |

|                       | DP IF                   | MEDIUM<br>PCB Traces,<br>Chip to chip If               | 8,1000<br>5,4000<br>2,7000<br>1,6200 | Fractional   | NRZ        | PCB<br>TRACES            | Embedded<br>Clock  | dual simplex           |

|                       | Ethernet<br>SGMII       | LOW<br>PCB Traces,<br>Chip to chip If                  | 1,2500                               | Fractional   | NRZ        | PCB<br>TRACES            | Separated<br>Clock | dual simplex           |

|                       | APIX3                   | Medium<br>Cable, medium range                          | 6,0000                               | Fractional   | NRZ        | STP/SPP                  | Embedded<br>Clock  | full duplex            |

#### Figure 3: APXpress SerDes data rates

The APX press-Link supports link rates of 4/8/16 or 32 Gbps which can be selected as required. It is also possible to use multi-lane setups to multiply the link rates accordingly or to create additional redundancy. In addition to the APX press link data rates, the APX press SerDes also supports many common data rates of today's application interfaces, for example an APIX3 backward compatibility mode with 6 Gbps, allowing backward compatibility with existing APIX3 systems. The structure of TX and RX always as a pair also enables extended test options, e.g. a built-in self-test and thus more precise quality checks even in the field.

### 6. Product innovations for Zonal Architectures – Trends in Connectors and Cables

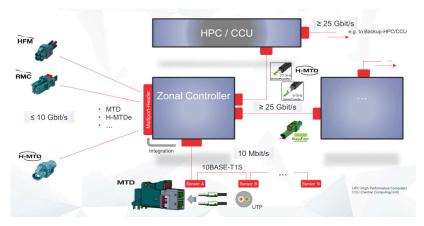

Zonal architectures consist of two types of modules that need to be connected to each other: A Central Computer and several Zonal Controllers. These Zonal Controllers act as collection nodes for data and signals from different sensors. Connectors must therefore fulfil two basic functions within zonal architectures:

- 1. Connection of all type of sensors to the Zonal Controllers for signal and data collection

- 2. Connection of Zonal Controllers to the Central Computer to enable transmission of the aggregated data at high rates.

To realise both, Rosenberger set the global standard by developing and publishing the H-MTD and HFM Interfaces in all relevant Automotive-standardisation committees worldwide. This strong drive towards standardisation enables all production and assembly steps to be completely automatised, beginning with the individual component of the connector, as well as the manufacturing of the cable assemblies and the installation of cables in the vehicle. This results in fully automatable architectures in the car, as Rosenberger has Cable-Assemblies and PCB-Headers both available out of fully automatic-production. In addition, there are several solutions and features available to support the fully automatic assembling of cable-assemblies into the vehicle.

Furthermore, the Rosenberger Multiport-Header covers point one from above, aiming especially for the transfer of data from the sensor to the zone's collection node. The Multiport-Header combines a wide variety of different connectors, differential as well as coaxial, shielded as well as unshielded, all in one housing. It is scalable and expandable. This means, regardless of the hardware, protocol and connectors in use, all cables from different sensors and applications

Figure 4: Rosenberger High-Speed-Connectors in Zonal Architectures – From Data Collection to the Central Computer

are bundled into just one connector within the Multiport-Header which then works as a collective node. This SMART and modular system reduces the number of connectors used and, at the same time, the overall cost and installation space of the module.

Starting from one zone, the aggregated data can be transmitted at a high frequency and data rate via a data highway to the Central Computer. The shielded differential product series H-MTD on SPP cable (Shielded-Parallel-Pair cable), which can transmit bandwidth up to 20 GHz, and the new glass fiber product series for the automotive sector GFC (Glass-Fiber-Connector), which can transmit a signific-

antly higher bandwidth and data rates by using optics, are particularly suitable for this purpose. The two high-performance product series can also be used for data transmission between the Zonal Controllers.

Rosenberger is also investigating how data connectors can be covered in the best possible way for the customer's particular application in terms of reliability. To realise this, it is necessary to break down signal integrity requirements depending on the protocol from the overall channel to the respective levels such as cable-assemblies, raw-cable and connectors. This approach allows "failure criteria" to be defined for individual components and therefore customers can reliably assemble the individual components for the respective protocol using a Modular-System and enable a Building-Block-Strategy at the OEM.

# 7. Use Cases

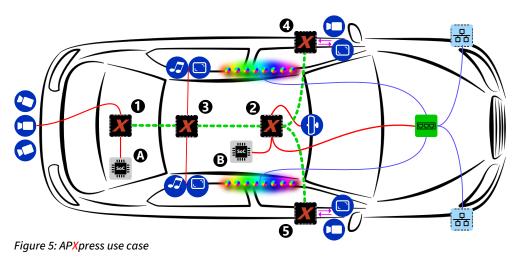

How flexibly APXpress can be used is explained step by step below using the use case shown in Figure 5.

Assuming two SoCs are used in the vehicle, they can be connected via PCIe using APXpress nodes (1, 2). One SoC acts as a PCIe master and the other as a slave. The SoCs do not both have to be in the same position but can be positioned

away from each other in the trunk and centre console as an example. Both SoCs can now communicate at 16 GT/s, for example. The imaginary point-topoint network can now be extended by a further node (3) at the height of the rear seats and thus control two rear-seat displays. The video content can be fed into the network in parallel to PCIe via DisplayPort on the side of the SoC in the trunk. The new node (3) routes the PCIe data streams and takes the two data streams for the displays.

These streams can be output here either via embedded DisplayPort or DSI, for example. If required, touch information can also be fed back to the rear SoC. sou

The application is now being expanded to include digital rear-view mirrors. Two new APXpress nodes (4, 5) are added for this purpose, which are located on the exterior mirrors. These nodes are connected to APXpress nodes (2) via the APXpress network. The camera data stream at the exterior mirror is also recorded via CSI, for example, and both camera

data are routed to SoC B. A display is also connected to each APXpress node (2, 4, 5) via e.g. DSI or LVDS for the rear-view mirrors (LORVM, IRVM, RORVM). Further three cameras are attached to APXpress nodes (1) via e.g. CSI. The three video streams are also output to APXpress nodes (2) to the SoC, which now processes all five camera streams (e.g. demosa-icing, cross-fading, bird's-eye view, etc.) and thus generates the content for the three mirror displays and transmits it to them.

In addition, Ethernet peripherals in the vehicle can be connected to APX node (2) via SGMII using an Ethernet switch, for example, which then makes ILaS/ISELED and other Ethernet peripherals such as headlights etc. from SoC A addressable to APX press node (1) here with RGMII or SGMII. Hypothetically, dynamic lighting scenarios could be generated here depending on the video content on the rear seat displays. It is also possible to set diagnostic access to the entire network at each of the five APX press nodes.

This flexible modular structure and expansion of the network is achieved by the virtual path technology and scalability of the APX press-Link layer. Different equipment variants, subsequent expansions and model upgrades can thus be easily implemented.

Authors:

Rosenberger Hochfrequenztechnik GmbH & Co. KG: Sebastian Dumann, Stephan Kunz Inova Semiconductors GmbH: Roland Neumann, Fabian Kluge