INAP562RAQ / INAP592RAQ

APIX3 Receiver with up to 12 Gbps for Video, Audio, Data & Ethernet

With OpenLDI/LVDS or MIPI DSI/CSI Video Output

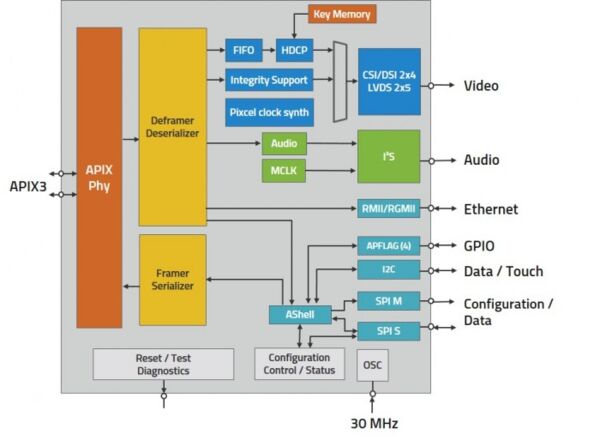

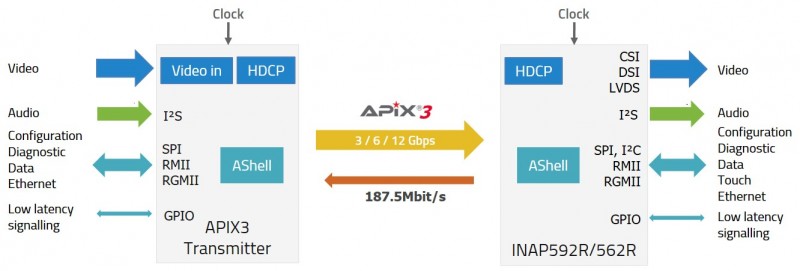

The INAP562RAQ/INAP592RAQ together with an APIX3 transmitter offers the next generation high-speed digital serial link over a Shielded Twisted Pair (STP) cable for display applications.

In dual lane mode its scalable physical layer allows bandwidth of up to 12 Gbps over distances of up to 10m at lowest EMI.

Both devices offer a configurable openLDI (LVDS), MIPI DSI, or CSI video interface to output one 24- or 30-bit native or VESA DSC compressed video stream. The INAP592RAQ additionally includes HDCP 1.4 decryption.

These devices provide a 10/100 Mbps Ethernet channel, completely independent Full Duplex Communication channels and general purpose signals. Using the internal AShell protocol, data transfers are protected by error detection and re-transmission mechanisms.

PRODUCT BRIEF

Subscribe to product update notifications: Login or register.

INAP562RAQ / 592RAQ Datasheet

The INAP562RAQ / 592RAQ Datasheet

is only available with a Login and signed NDA.

Contact Inova for more NDA information.

INAP562RAQ / 592RAQ User Manual

The INAP562RAQ / 592RAQ User Manual

is only available with a Login and signed NDA.

Contact Inova for more NDA information.

• Flexible physical layer supporting

– 1.5 Gbps, 3 Gbps or 6 Gbps downstream

– 187.5 Mbps per lane upstream

– Dual lane support for 3, 6 and 12 Gbps

downstream

• HDCP 1.4 support (INAP592R only)

• Dual MIPI/LVDS interface to support

– DPHY 1.2 with up to 1.5 Gbps per lane

– DSI 1.2, CSI 1.1

– Support for combined 2x4 operation

– Support for DSC tunneling

– LVDS interface for single and dual use

– Support for JEIDA and VESA format

– Support for 18/24/30 bit color depth

– Support for combined 2x5 operation

• Uncompressed video resolution examples

– 2880x1080x24bit, 60Hz

• Configurable full-duplex communication

channel for Data, Ethernet or GPIO

– RGMII, RMII or MII interface for

10/100Mbps Ethernet

– SPI data interfaces

– 4x GPIO for direct signaling over the

AShell (APFLAG)

• Embedded AShell protocol

• Audio interface I2S

– supports 16/24/32 Bit word length

– supports 44.1 kHz / 48 / 96 kHz sampling

– Time Division Multiplexing (TDM) for up

to 8 channels

• Diagnostic Features:

– Continuous link monitoring

• APIX2 backward compatible

• Pin-to-pin compatible to INAP561R and

INAP591R

APPLICATION NOTES |

DESCRIPTION |

DOWNLOAD |

|---|---|---|

AN301 |

APIX3 Transfer Channel Requirements |

|

AN302 |

Measurement setup and procedure with the HSD connect |

|

AN303 |

Design and Layout Guidelines for APIX3 |

|

AN304 |

Schematics Guideline INAP562/592RAQ / INAP563/593RAQ |

|

AN307 |

Line Driver Setup for INAP5xxTAQ in APIX2 mode |

|

AN309 |

APIX3 Compliance |

|

AN310 |

APIX3 Start-up and Diagnostic |

|

AN311 |

INAP5xxTAQ/RAQ Quickstart Guide |

|

AN312 |

APIX3 out of band signaling (OOB) over STP |

|

AN316 |

Analyzing DisplayPort™ AUX Traffic |

|

AN317 |

INAPxxT/R Register Dump |

|

AN318 |

INAP567TAQ/597TAQ Information for functional safety relevant applications |

|

AN319 |

INAP565TAQ Information for functional safety relevant applications |

|

AN320 |

APIX3 – System ESD considerations |

FORMAT |

ZIP |

CONTACT |

BXL |